日志

原理图规范

2020-09-16 23:02

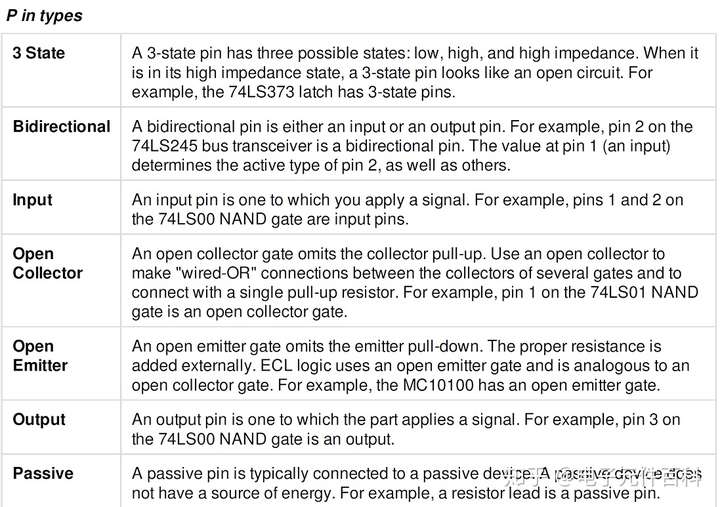

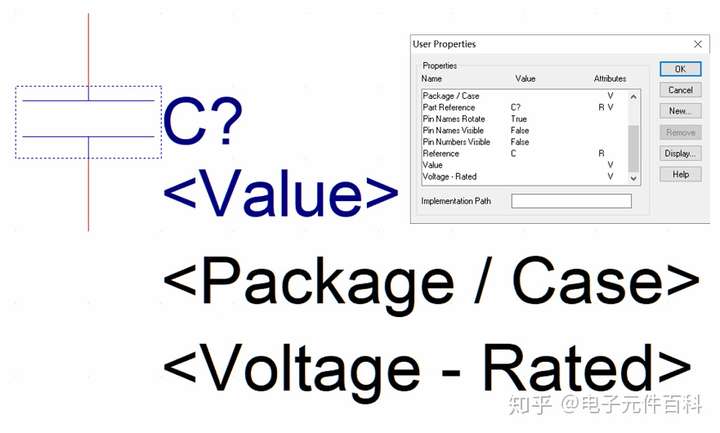

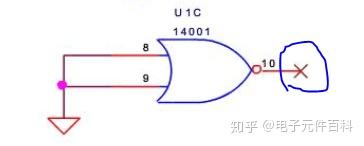

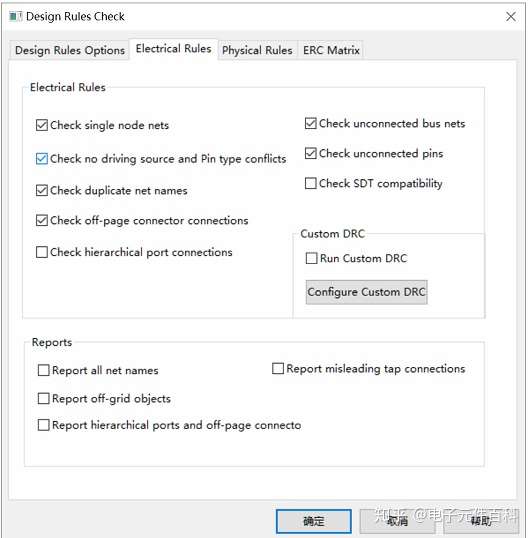

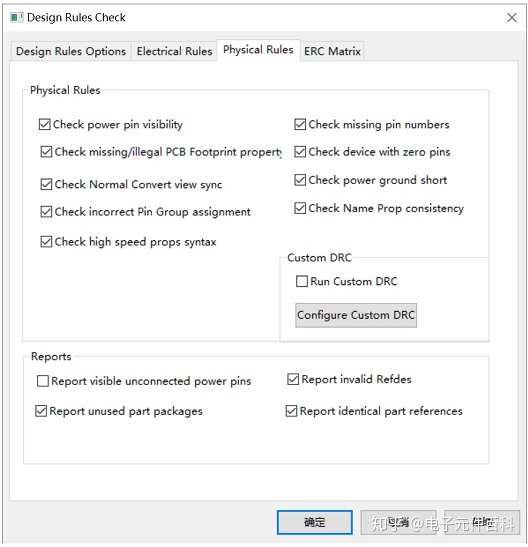

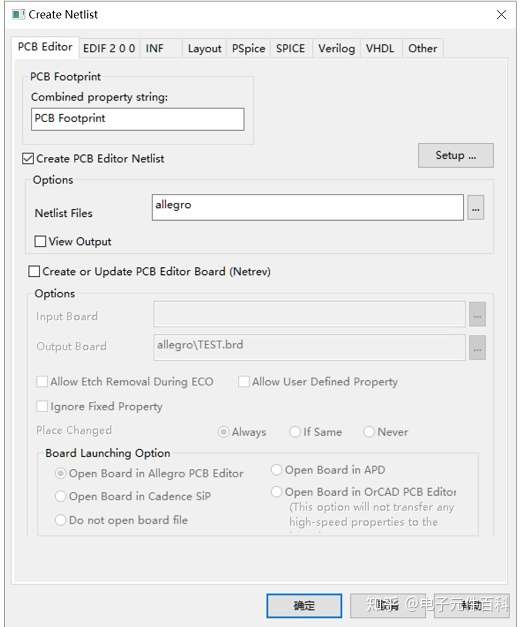

转载自:https://zhuanlan.zhihu.com/p/132673944 原理图是硬件设计的基础,为了原理图规范、清晰、准确、易读,特对原理图的结构、字体、元件、注释等作出规范(不涉及具体电路设计)。 OrCAD Capture CIS是Cadence旗下一款强大且方便易用的原理图工具,本文基于其成熟版本16.6对原理图设计规范进行说明,并在附件中提供了原理图模板文件TEMPLATE.DSN,以及原理图设计实例文件TV_1V0_SCH_1V1.DSN,以供设计时参考。 1、原理图dsn文件命名 项目名称_SCH+原理图版本 示例: TV_1V0_SCH_1V1 TV_1V0为项目名称,1V0为项目版本,1V1为原理图版本。 因dsn文件名不允许包含“.”,故版本号1.0则定义为1V0。 当原理图更新时,需要升级原理图版本号,不涉及PCB的改动则升级小数点后的数字,如1V0升级为1V1,设计PCB的改动则升级小数点前的数字,如1V0升级为2V0。 2、原理图工具使用 2.1 原理图工具 原理图采用Cadence 16.6 OrCAD Capture CIS绘制,软件版本信息如下图所示。 因用到了CIS元件库,故必须使用OrCAD Capture CIS,而不能使用OrCAD Capture。  2.2 OrCAD Capture CIS的配置 2.2 OrCAD Capture CIS的配置2.2.1 Options》Design Template(设计模板)配置更改如下,其余均按软件默认设置。 当新建Design时,软件会按照配置的内容自动填充。 2.2.1.1 Title Block Organization Name填写公司名称 Document Number填写项目名称 Revision填写原理图版本 Symbol》Library Name选择CAPSYM.OLB Symbol》Title Block Name选择CAPSYM库中的TitleBlock1  2.2.1.2 Page Size选择Inches B,以便在A4纸上打印。 2.2.1.2 Page Size选择Inches B,以便在A4纸上打印。3、框架 此节说明原理图的组成,具体可参考附件的Template.dsn。 3.1 封面 第1页是封面,包括项目名称、修改历史、以及整个原理图的页面列表。 对于每一次更新版本,均应在修改历史中给出具体的修改内容,并附带修改原因。 3.2 系统框图和电源分配图 第2页系统框图应画出系统各个模块及连接关系,电源分配图则给出电源从输入到输出各种电压的分配图(建议标出各路电源的最大电流值)。 3.3 其他的说明信息及实际电路图 如需说明其他信息,如GPIO的配置表,则可以放在第3页,如无则第3页开始为实际电路图。 4、页面 页面应简洁,页面对象如元件之间的间隔、各网络连线等应以简洁为原则,禁止元件重叠、连线混乱。整个原理图中,不允许有空页面,如有应删除。 4.1页面的命名:页码_页面Title 如果原理图页数少于10页,则页码可以从1至9,否则页码必须从01开始,OrCAD软件按照页码自动对页面进行排序。 示例:01_Cover 4.2 页面对象 页面对象指页面中的元件、连线、网络等。 4.2.1 元件原理图封装 常用元件封装如电阻、电容等,建议按照标准的画法,具体的可参考OrCAD软件自带的库(默认库文件位置:C:\Cadence\Cadence_SPB_16.6-2015\tools\capture\library)。如果是特殊的元件,可参考厂家的规格书。 元件引脚建议按功能分类画在一起,如电源、控制、数据等,而不是按照引脚的序号。输入引脚放在元件的左边,输出引脚放在元件的右边,电源引脚在上方,地引脚在下方。如果元件的引脚较多,建议分成多个part,按字母A、B、C等编号。引脚应和PCB封装一一对应。 引脚命名应能表征其功能,可参考元件规格书,名称字母均大写,如果是低有效,则加后缀“#”,如Reset#。 创建元件原理图封装时,为了DRC检查,需要设置引脚pin的TYPE,各TYPE的解释如下图,电源和地pin脚的TYPE设置为passive,不可按OrCAD软件的推荐设置为Power。如果设置为Power,则电源的pin名称同时也是全局域的网络名称,各元件之间的电源和地网络很容易混乱。  4.2.2 元件参数 4.2.2 元件参数元件有很多参数,原理图上应标注出元件的重要参数,便于理解原理图。 元件值Value应选一个最基本的参数(如电阻选阻值),且均标注在原理图上。如果此元件不上件(空贴),Value应设置为NC,此元件同时应添加属性“BOM_IGNORE”=”TRUE”,这样制作BOM时,软件会自动排除此元件。 元件的其余的重要参数也应在原理图上显示,如大电容的耐压、大电感的额定电流等。 对于阻容感等的PCB封装,选一个元件数最多的封装为默认封装如0402不标注,其余封装如0603、0805等均应在元件旁标注封装名。 对于元件参数显示的更改,如需要把所有0603封装的电容,在原理图上显示封装0603和耐压,可把0603电容所用的原理图封装Part的封装和耐压Display属性改为Visible(如下图)。  4.2.3 元件位号 4.2.3 元件位号位号包含前缀和数字序号,各元件的前缀请参考下表,表中未列出的元件按习惯指定前缀,或根据其英文名缩写来确定。数字序号如果是全新项目,建议按递增编号,如R1 R2 R3等,如果是改版项目,或者需要和参考设计保持一致(如考虑PCB复用),则应保留原来的编号,只有新增的元件才重新按递增编号。  4.4 元件之间的连接 4.4 元件之间的连接同页之间用导线(wire)、总线(Bus)和网络名(net alias)连接。尽量把属于同一电路的元件放在同一页,两个元件不能直接连接,中间必须有连线,同时连线尽量避免交叉(避免歧义)。如果某个元件的引脚无连接,则在此引脚上需要添加“X”,以表明此Pin悬空,如下图所示。  不同页之间用跨页连接符(off-page connector)连接。跨页连接符旁边需标注起交叉引用页码,如果需要更新,需先删除原标注的页码,再重新标注。具体操作步骤为,在工程管理窗口选择原理图文件(.dsn),再点击菜单Tools》Annotate,出现如下图对话框,删除操作选择“Action》Delete intersheeet References”,重新标注选择“Action》Add intersheeet References”。 不同页之间用跨页连接符(off-page connector)连接。跨页连接符旁边需标注起交叉引用页码,如果需要更新,需先删除原标注的页码,再重新标注。具体操作步骤为,在工程管理窗口选择原理图文件(.dsn),再点击菜单Tools》Annotate,出现如下图对话框,删除操作选择“Action》Delete intersheeet References”,重新标注选择“Action》Add intersheeet References”。 4.5 网络命名 4.5 网络命名网络名称均用大写字母和数字,各单词之间用“_”连接,名称应体现信号的功能、参数等,如5G_TX0。如果是此网络是低有效,建议加后缀”_n”,如RESET_n。 4.6 注释 注释指用文字等对电路进行说明,如对电路Layout的说明,模块功能的说明等。 注释文字应准确、简洁,避免歧义。如果用图形则需要区分正常的元件和注释添加的图形,如注释图形加一虚线框。 另同一页中可能出现多个小功能模块,为了分割这些模块,建议用虚线分割。 5、DRC DRC(Design Rules Check)是按照ERC Matrix设定的规则来对原理图进行检查,比如单网络、两个输出引脚连在一起。要求DRC报告中无错误项,警告项需逐个确认对电路无影响。 具体操作为,在工程管理窗口选择原理图文件(.dsn),再点击菜单Tools》Design Rules Check…,弹出DRC对话框,按下图设置,确定并运行DRC,最后查看DRC报告。    6、网表 6、网表网表文件标注了各元件的封装、各网络的连接关系,PCB根据网表调入元件的封装,并定义各元件Pin脚之间的连接。导出网表的过程中,软件会自动检查原理图,如封装、pin和网络,应保证网表导出无错误提示,对于警告也应逐一确认。 对于PCB工程师来说,有网表即可画PCB,如有dsn原理图文件则更加方便,但会有泄密的风险,对于公司内部,可以给原理图dsn文件,对于公司外部,如果担心,则应只给网表以及PDF格式的原理图文件。 不同的PCB工具,网表的格式不同,应按照PCB工具导出正确的网表。公司常用的PCB工具有两个 Cadence Allegro 16.6和PADS9.5。 Cadence Allegro 16.6网表导出步骤为,在工程管理窗口选择原理图文件(.dsn),再点击菜单Tools》Create Netlist弹出对话框,按下图设置,点击确定,即在dsn文件同目录下生成网表文件。  PADS 9.5导出网表步骤和Allegro类似,但按下图设置。 PADS 9.5导出网表步骤和Allegro类似,但按下图设置。 7、BOM 7、BOMBOM(Bill of Materials)为元器件清单,对于元器件的选择应遵循如下原则: 1) 普遍性原则:所选的元器件要被广泛使用验证过的,尽量少使用冷偏芯片; 2) 高性价比原则:在功能、性能、使用率都相近的情况下,尽量选择价格比较好的元器件,减少成本; 3) 采购方便原则:尽量选择容易买到,供货周期短的元器件; 4) 持续发展原则:尽量选择在可预见的时间内不会停产的元器件; 5) 可替代原则:尽量选择pin to pin兼容种类比较多的元器件; 6) 向上兼容原则:尽量选择以前老产品用过的元器件; 7) 资源节约原则:尽量用上元器件的全部功能和管脚。 对于空贴的器件(Value=NC),应添加属性“BOM_IGNORE”=”TRUE”,否则其仍然会出现在BOM中。 BOM导出应无错误提示,对于警告也应逐一确认。对于导出的BOM应检查,如元件型号、封装和描述是否正确、元件是否有遗漏等,另外对于物料应尽量统一,减少物料的种类,便于采购和物料管理,如1K 5%的电阻有两种封装0201和0402,则可以统一成同一封装。 具体步骤为,在工程管理窗口选择原理图文件(.dsn),再点击菜单Reports》Bill of Materials》Standard,按下图设置,BOM导出为Excel文件,再按照公司BOM模板整理。 BOM命名为“项目名称“+“_原理图版本”+”_BOM版本“,如TV1.0_SCHV1.0_BOMV1.0.xls。  附件(请关注微信公众号“电子元件百科”,回复“原理图设计规范”获得下载链接。): 附件(请关注微信公众号“电子元件百科”,回复“原理图设计规范”获得下载链接。):1、Template.dsn 2、TV_1V0_SCH_1V1.DSN 参考资料: 1、CSDN 易安_草上帆 硬件原理图设计的若干规范 [backcolor= transparent]https://blog.csdn.net/qq_419193[backcolor= transparent]52/article/details/83475782 2、百度文库 原理图设计规范 [backcolor= transparent]https://wenku.baidu.com/view/3e[backcolor= transparent]4c5a400722192e4536f6c6.html 3、Cadence OrCAD Capture User Guide 位于Cadence安装目录内,默认路径:C:\Cadence\Cadence_SPB_16.6-2015\doc\cap_ug\cap_ug.pdf 4、Cadence OrCAD CIS User Guide 位于Cadence安装目录内,默认路径C:\Cadence\Cadence_SPB_16.6-2015\doc\cisug\cisug.pdf |

下一篇: 无

上一篇: 无