|

|

U/j+\�Kc~�

MIPI Layout 说明 LVAnZ'h/|

前言: ,0fYB*jk��

随着新的总线协议不断提高信号速率,如今的PCB 设计人员需要充分理解高速布线的要求并控制PCB 走线的阻抗;对于MIPI 信号来说,PCB 走线不再是简单的连接,而是传输线。 k<.VR"I

p�

MIPI 属于差分信号(Differential Signal),差分信号的优点在于更好的抗干扰性、更高的速率和更少的信号线连接。 I��A(�+}V�

关键词: l

�]CnLqf&

线对:指一组差分线,如CLK+和CLK- , DN1+与DN1- 1 �G���B��

1 差分阻抗控制: �MU#$tXmnC

PCB 走线的关键参数之一是其特性阻抗(即波沿导线传送时电压与电流的比值)。PCB上导线的特性阻抗是衡量高速电路板设计的一个重要指标,高速信号走线的阻抗和器件或信号所要求的特性阻抗必须一致。 如阻抗偏差过大或不一致,会使其信号失真,造成不工作或不稳定;所以在高速线路板上的导线阻抗值应控制在某一范围之内,称为“阻抗控制”。 ?5�U�b&{��

影响PCB 走线阻抗的因素主要有: 走线的宽度、走线之间的间距、导线厚度(铜厚)、绝缘介质的介电常数及厚度、是否有参考平面(地层或电源层)等。这些参数与设计和PCB制作本身都息息相关,所以不仅设计上要做到,在PCB 发包时也需要告诉PCB 厂家哪些是差分线,由厂家在制作时也进行控制。 @;P\`[�(�*

MIPI 的差分线阻抗控制标准是100 欧姆,误差不能大于±10%。 O~u�@�J�'4

1.1 PCB 叠层分析: ufc_m�4PN

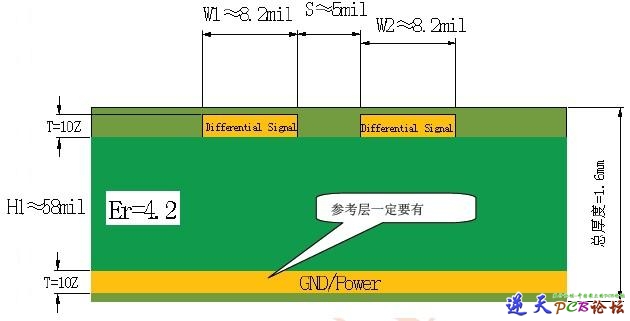

两层板上的MIPI 走线典型的叠层结构如下: =2tl149m/z

如上图,PCB 传输线通常由信号走线、一个或多个参考层和绝缘材质组成; "P�tOe[Xk� 如上图,PCB 传输线通常由信号走线、一个或多个参考层和绝缘材质组成; "P�tOe[Xk�

W1/W2 为差分线对走线的宽度,S 为差分线对走线之间的距离,T 为导线的厚度(铜厚),H1 为绝缘介质厚度,Er 为绝缘层的介电常数。 C+<�z��;9`

1.2 计算差分阻抗: �+f]\>{�o4

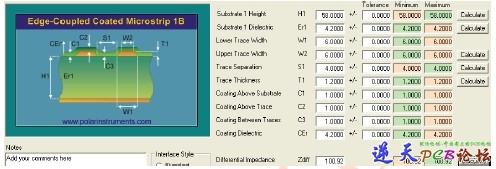

差分阻抗需要用仿真软件来计算(推荐软件:Polar Si9000V7.1),计算好后再依据计算结果来走线。 以下是1.6mm 厚度两层板的差分线阻抗控制实例: ;=oGg%@a�P

1、W1/W2=6.0mil,S=4mil,T=1OZ,H1=58mil,Er=4.3,其阻抗等于100.92 欧姆。 *�Jm�U",X�

2、W1/W2=8.2mil,S=5mil,T=1OZ,H1=58mil,Er=4.3,其阻抗等于103.55 欧姆。 GTBT0$9�g.

3、W1/W2=12mil,S=6mil,T=1OZ,H1=58mil,Er=4.3,其阻抗等于101.96 欧姆。 �+E�-�f��

2 Layout 说明: �!t��r�

/$

2.1 要求: F)��Q�j<�6

A、参考层: MIPI 信号线下方一定要有参考层(推荐用地层),且一定要保证参考层的连续性(即在MIPI 信号线下方的参考层不能被分割或有间隙,不能被其它走线截断),最好是有一整片的地层,如果做不到,至少要保证MIPI 信号线下方的参考层比MIPI 信号线每边要宽4W 以上(W 即MIPI 信号走线宽度)。 参考层对走线阻抗会产生影响,仿真软件里的计算都是假设有一个参考层的 =��S|^p��N

B、等长:MIPI 线对之间的长度误差是要控制在10mil 以内,线对与线对之间的长度误差控制在200mil 以内;等长是为了保证两个差分信号能同时到达接收端。否则会接收不到正确的数据 A��Q��e~F

C、对称性:MIPI 线对要始终保持等长和等距(依照仿真结果)。 对称是为了保证走线阻抗一致,减少反射。对称性不好会使信号失真,导致不稳定或无图 u9��~R��D�

D、远离干扰:MIPI 线对之间要保持至少2W 以上的间距,MIPI 信号线应远离其它高速信号(如并行数据线,时钟线等),至少保持3W 以上的距离且绝不能平行走线。 对开关电源这一类的干扰源更应远离 u,�Rhm��-`

E、另外 MIPI 信号线尽量不要打过孔,如有过孔则线对上的两根线都要有(保持对称性),信号线换层后参考层也要也要靠近信号线的过孔打孔换层 eH�y.<V��X

F、MIPI 差分走线的设计中最重要的规则就是匹配线长,其它的规则都可以根据设计要求和实际应用进行灵活处理。 |Je+�y;P7�

2.2 举例说明: R�404\XGL

以下为MIPI 差分线走线要求和参考 xgQ]#�{�tG

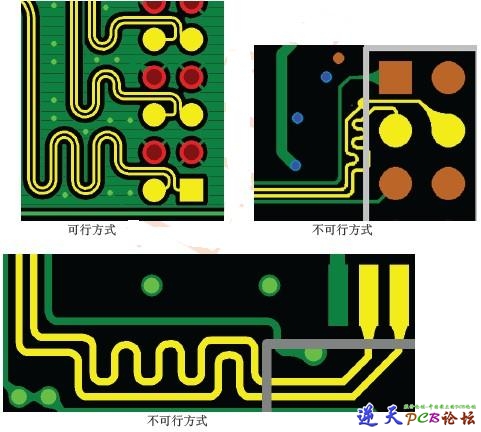

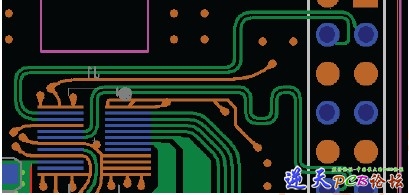

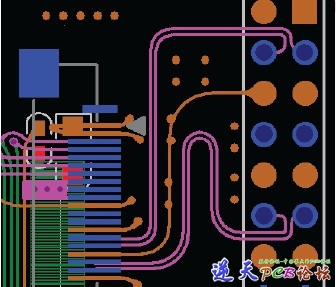

a 、走线时,必须保证等长和对称性: A�[�.5B��i

b 、做等长时蛇形线不应太密集,应保证在4X 线宽: �{�aRZBIv� b 、做等长时蛇形线不应太密集,应保证在4X 线宽: �{�aRZBIv�

3 总结: @�N0(�%o&� 3 总结: @�N0(�%o&�

1、了解差分信号的阻抗,为 Layout 做好准备; Q8s�CI An{

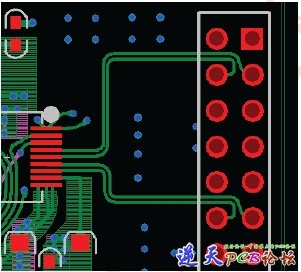

2、优先对关键信号/高速信号进行走线,尽量在Top 和Bottom 走线,划分好参考层,地线上多加地孔; 6�8v59)0�U

3、差分线对必须对称、等长、等距、平行,了解差分线对长度误差应小于10mil,差分线对之间的长度误差小于200mil; *;I F^�u1

4、做等长时,要注意对称性,绕蛇形线时不能太密集,应为4W,等长尽量在焊盘附件解决,以倒角形式来走线,不能随意改变线宽和线距; �$3��C$])k

5、避免直角走线,以免产生反射,影响高速传输性能。 8;�r7ksE~�

4 仿真软件界面(Polar Si9000V7.1) �=*u:@T=d5

5 设计实例 l��8_�TeO� 5 设计实例 l��8_�TeO�

��al3[Ph5G ��al3[Ph5G

Pv(icf�

l|

|