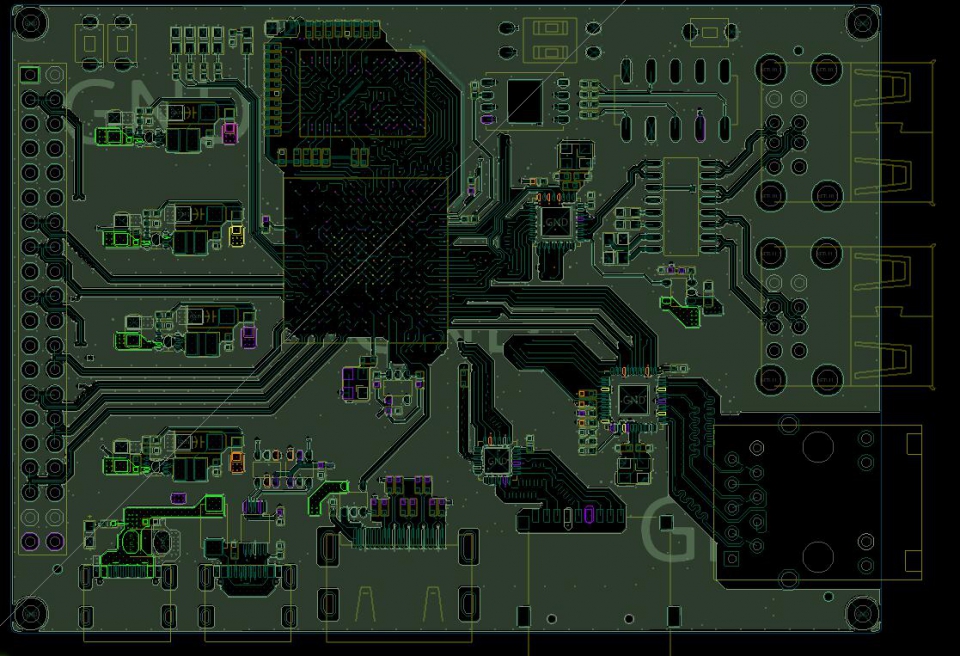

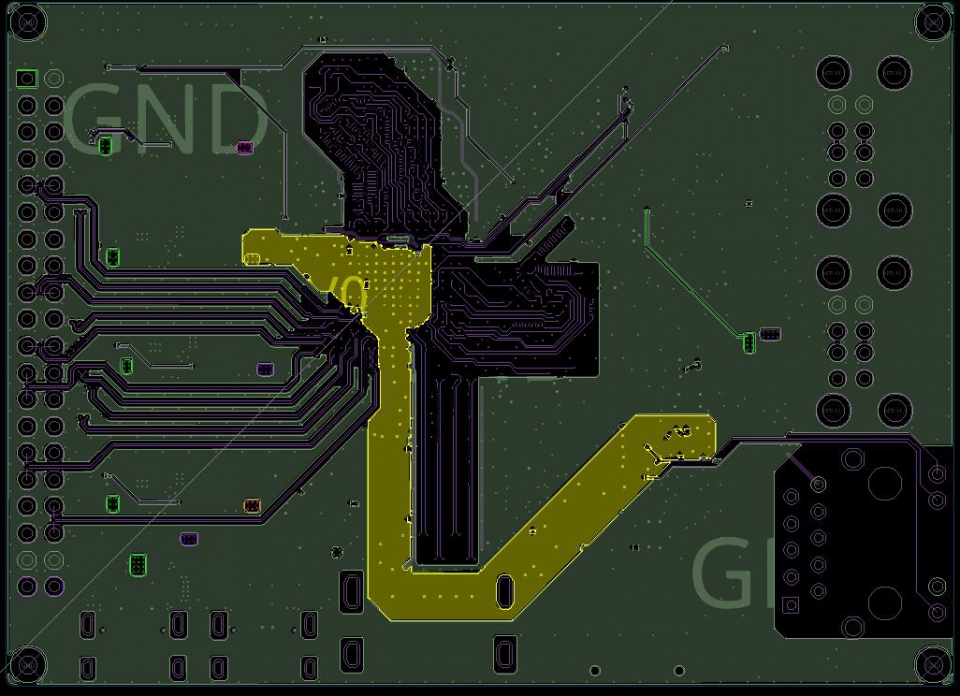

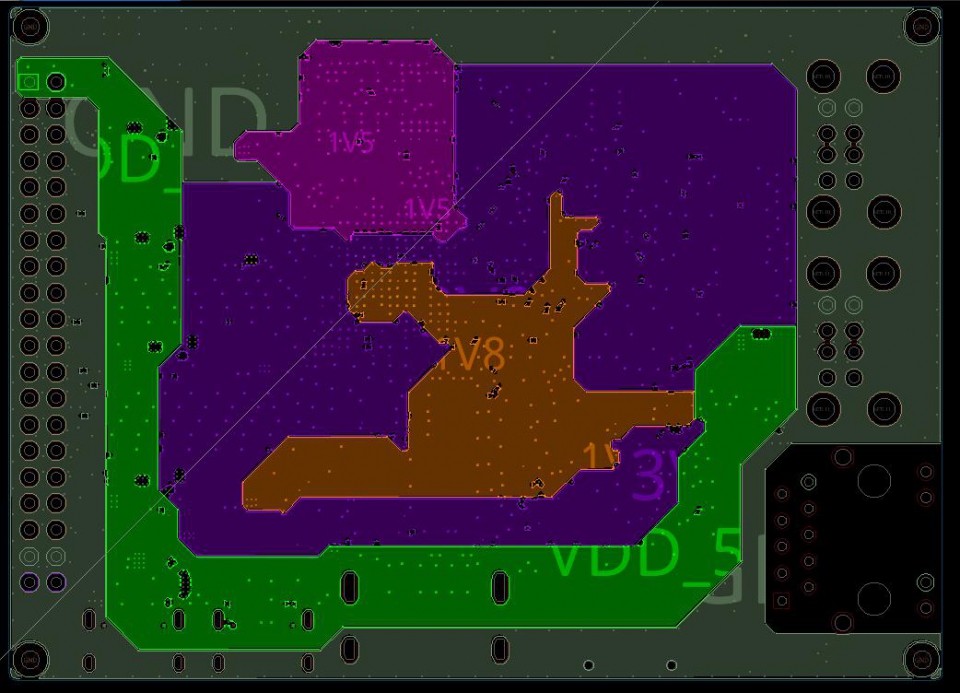

画这个案子期间,看了老师讲RK3399的

原理图还有本案子的原理图做了笔记,看了些RK3399,RK3588一些LAYOUT的板子,结合

经验画的本案子。

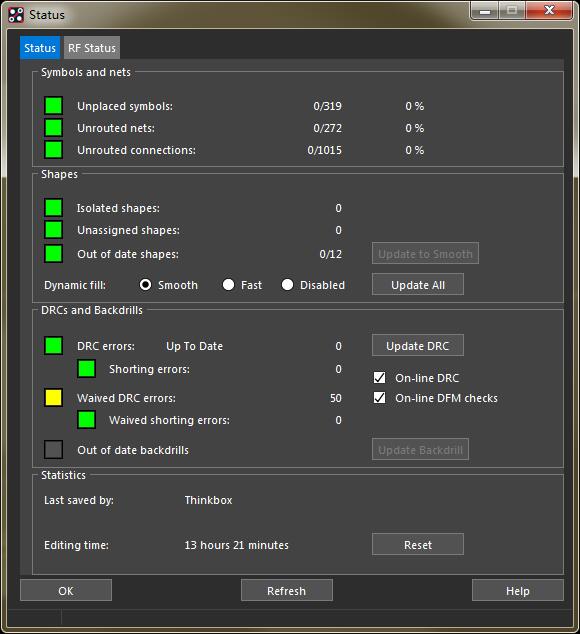

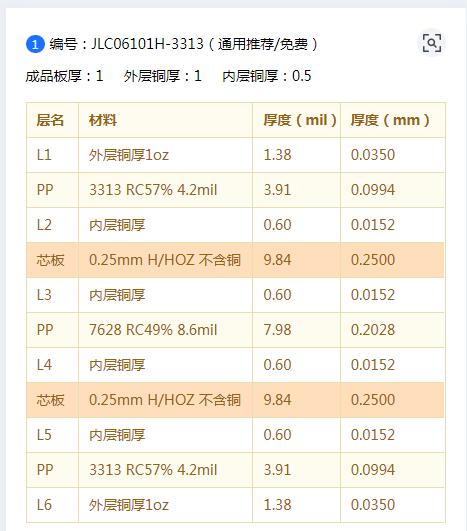

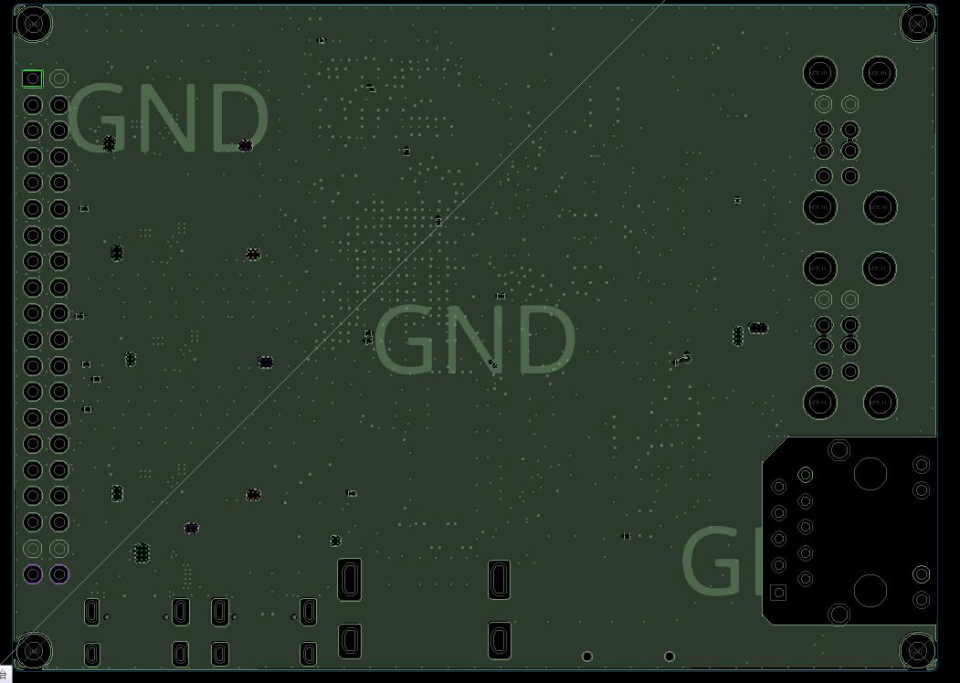

第一次画这种高速板,第一次计算阻抗,第一次用Allegro软件,有低速板的LAYOUT的经验,看过老师之前一天学习Allegro视频,看过老师的SI9000阻抗计算

软件教程视频。

希望老师点评一下还有哪些地方有错误的,没有考虑到的,或者有更好改进地方的。

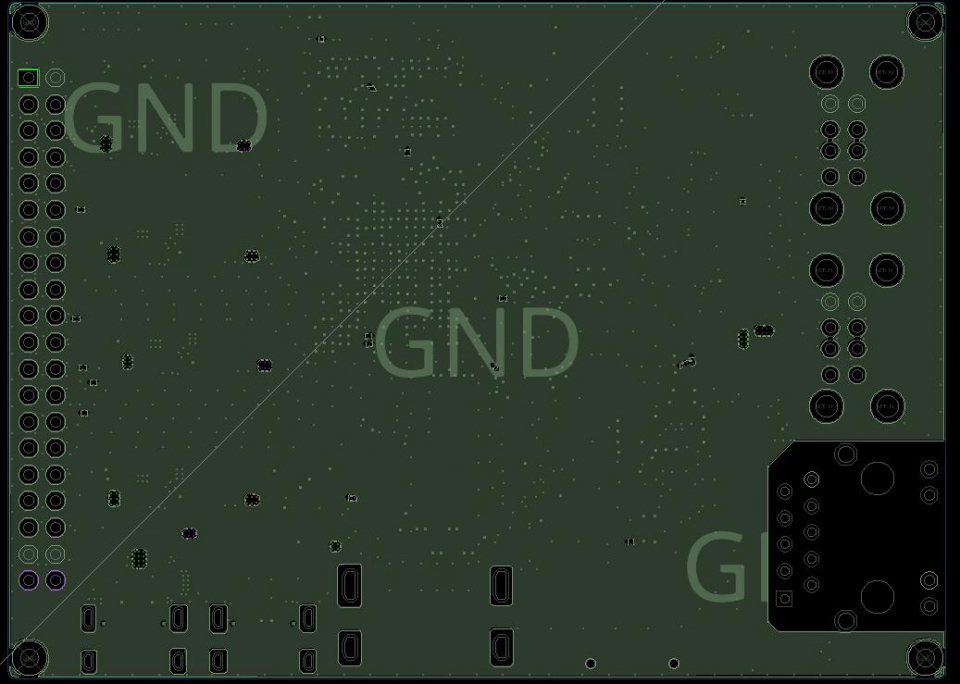

这个案子除了叠层缺陷以外,是否可以达到

量产的程度,就是想知道自已是否可以去画些高速板的能力了。谢谢!

项目2所有

资料打包

Cadence_project2_XC7Z010_ntpcb3356619.rar (12890 K) 下载次数:2

Cadence_project2_XC7Z010_ntpcb3356619.rar (12890 K) 下载次数:2 [ 此帖被ntpcb3356619在2023-06-01 16:04重新编辑 ]